# Circuit design for IO extension card

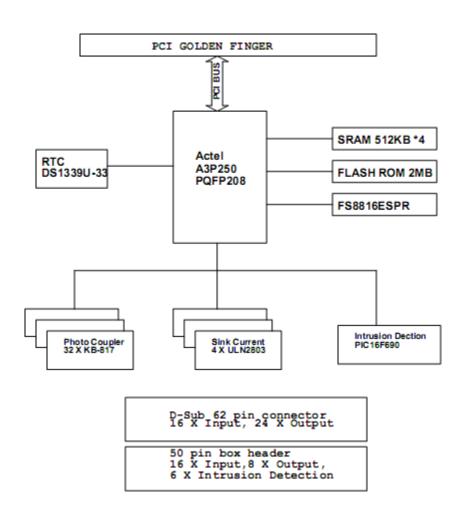

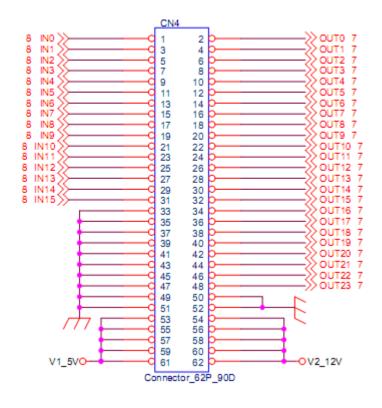

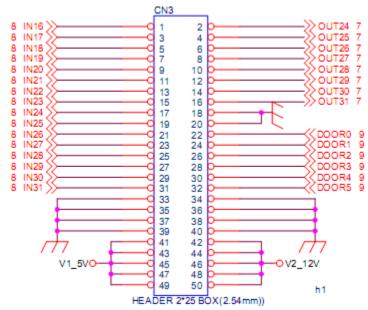

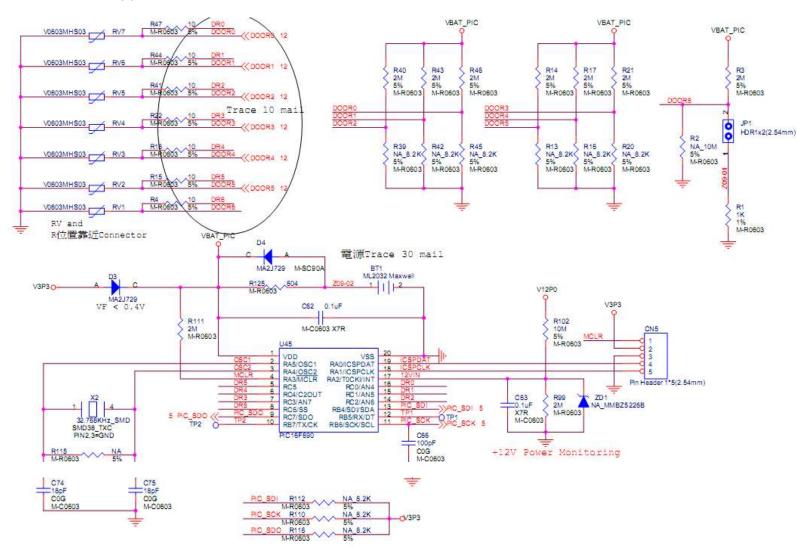

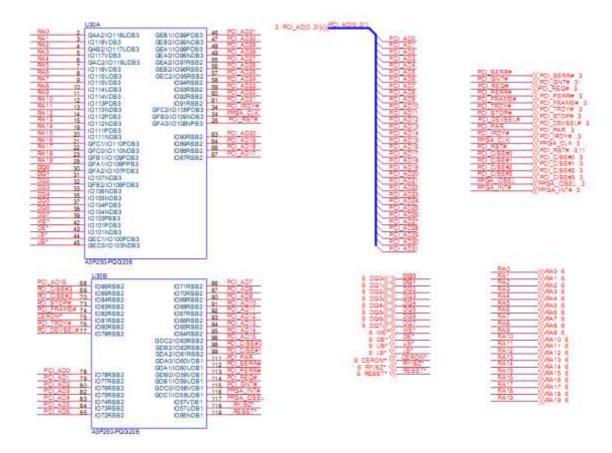

The block diagram below gives an overview of the product and the components in the IO extension card. The extension card has an Actel prosaic 3 FPGA connected to the CPU via a PCI bus. The FPGA has a battery backed RTC, 4MB or battery backed SRAM for storing state information of the system at all times and data recovery after a crash, a 2MB flash memory, an FS8816ESPR chip for authentication of embedded software, a battery powered intrusion detection system using the PIC16F690 microcontroller, photo-coupler isolated 50 pin connector with 16 outputs 8 inputs and 6 pins for intrusion detection and a 64 pin D-sub connector with 16 input and 24 output pins.

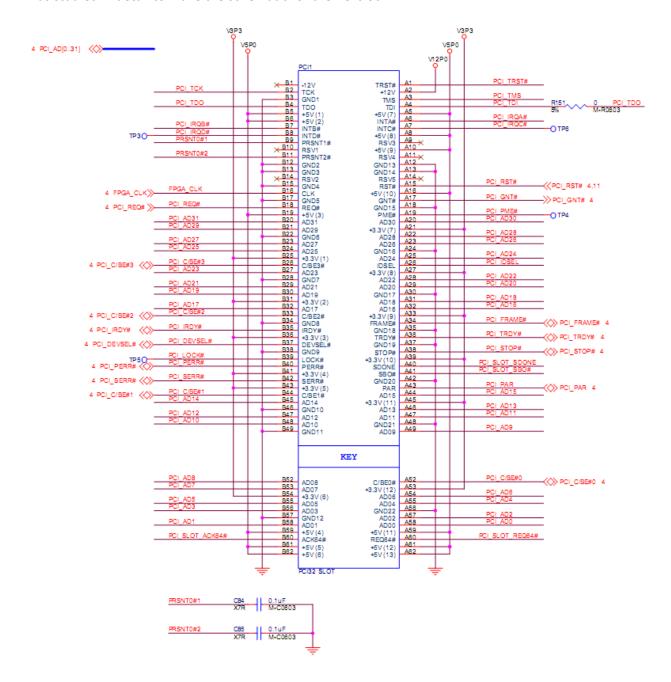

#### **PCI Connector**

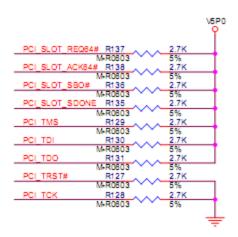

The design for the PCI connector was done referring to the PCI Local Bus specifications (ftp://ftp.adm.com.ua/pub/doc/pci21.pdf) published by the PCI special interest group. The specification was studied in detail to make the schematic for the PCI slot.

| PCI_IRQA# | R139 0                    |                             |

|-----------|---------------------------|-----------------------------|

| 001 1000# | 5% M-R0803                | FROM BUTH                   |

| PCI_IRQB# | R140 NA<br>5% M-R0803     | FPGA_INT# >>> FPGA_INT# 4   |

| PCI_AD21  | R133 A A NA 100           |                             |

|           | M-R0803 1%                |                             |

| PCI_AD20  | R134 NA 100<br>M-R0803 1% | •                           |

| PCI_IDSEL | R132 100                  | FPGA_IDSEL_>>> FPGA_IDSEL 4 |

| _         | M-R0803 1%                | // FPGA_IDSEL 4             |

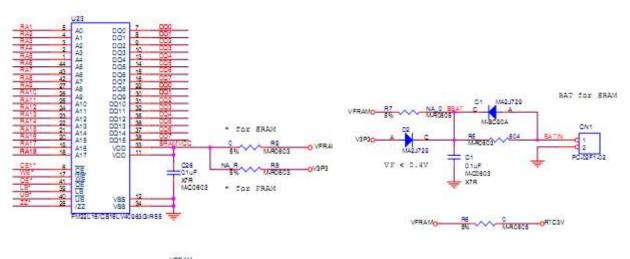

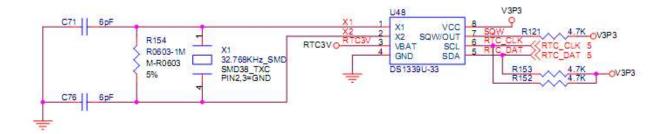

The SRAM, PIC 16F690 based intrusion detection system, Actel Proasic3 FPGA and the DS1339 RTC were made as suggested by their datasheets and the board requirements.

The schematics drawings were made using the Cadence OrCad capture CIS design tool. This involved making a library of all the components used in the design. Considerable proficiency was acquired in making schematic drawings using the tool and circuit design skill were acquired during the course of the design process. Having complete knowledge of the FPGA firmware before hand was useful in designing the circuit.

# 2MB Flash memory

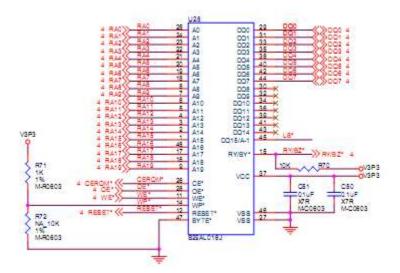

## 4MB battery backup SRAM

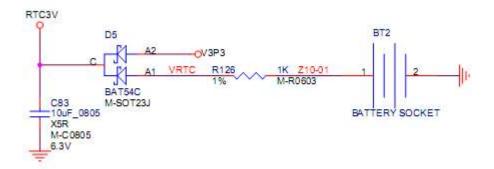

### Battrey backed up RTC circuit

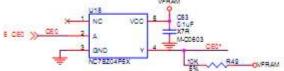

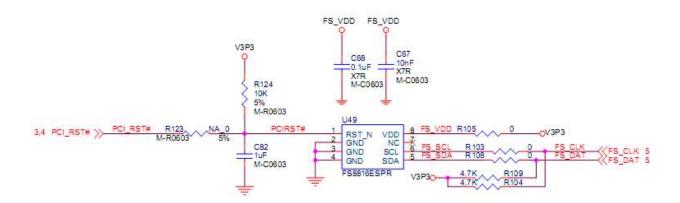

### FS8816ESPR for embedded software authentication

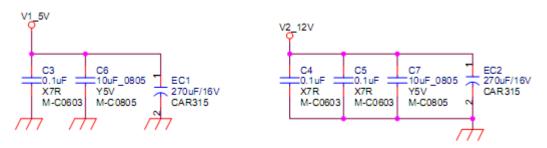

Power supply decoupled to ground for immunity to noise.

The different capacitor values are used to filter out noise at different frequencies.

### Battery powered intrusion detection circuit

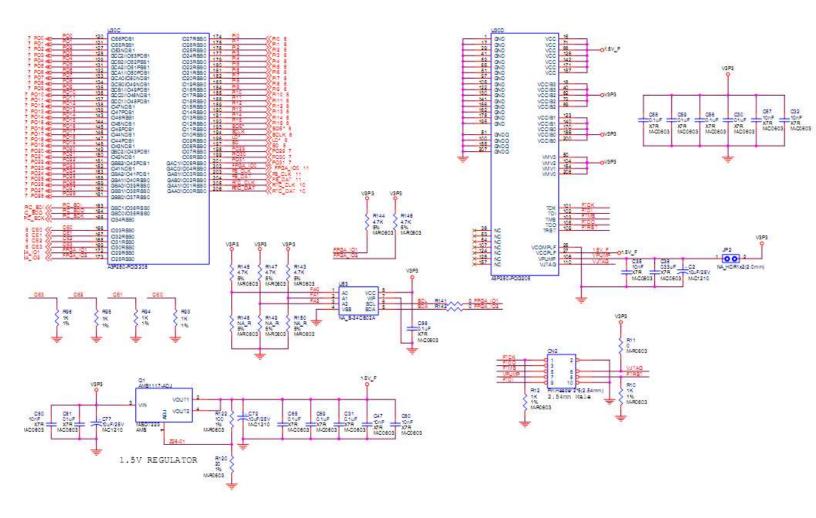

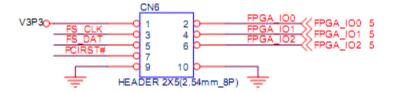

#### FPGA connections:

Connections for the FPGA and the PCI slot and the SRAM and the Flash memory are in the above figure and connections with the rest of the system are in the figure below. The FPGA forms the heart of the system here. The FPGA has the frimware of a PCI bus and the frimware also interfaces with everything else on the card like the SRAM, Flash memory, the FS8816ESPR and the RTC. The OS on the CPU sends commands to the extention card via the driver developed for the card and thus sends commands to the fpga which intrurn controlls the whole system. The reason for using an FPGA is for security and also realtime IO demands. The FPGA firmware is unique to the system and makes the customers software safe from piracy also the realtime IO required in the games for eg. Running a stepper motor for the slot machine can easily be done via the FPGA.